ADC(Analog to Digital Converter)를 만들기 위한 첫 단계는 continuos time signal인 아날로그 신호를 일정한 시간간격으로 sampling하는 것입니다. 이를 위한 Sample and Hold Circuit을 알아보겠습니다.

Sample and Hold를 하기 위해서 우선 Switch가 필요합니다. MOS TR을 triode/cut-off region에서 동작시키면 스위치로 사용할 수 있습니다.

이때 On-Resistance는 다음과 같으며 이 값이 작을때 turn on 상태일때 신호를 더 잘 전달시킵니다. W/L 값을 작게 해야 Ron 값을 줄일 수 있습니다.

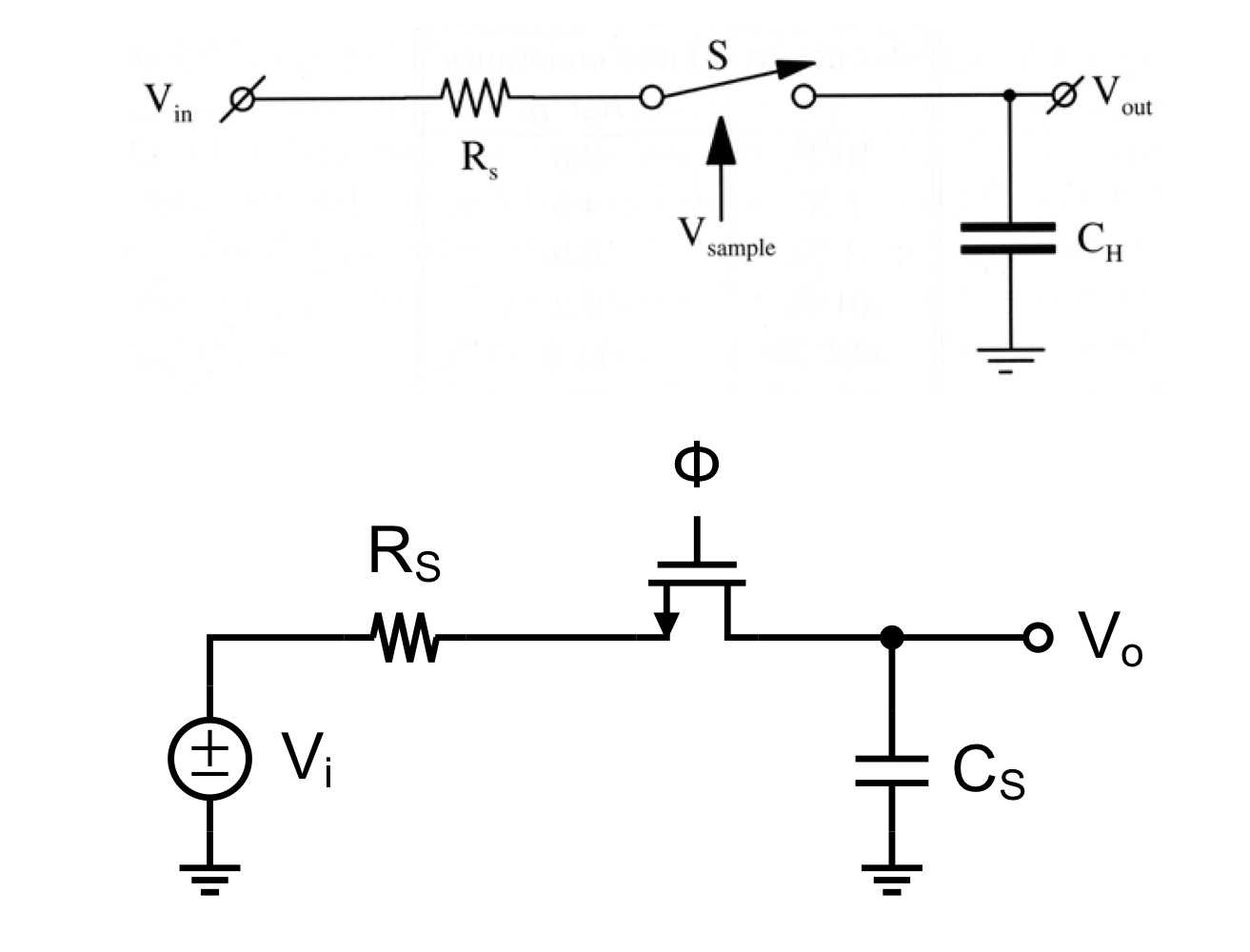

1. Switch on - Sampling(tracking) Vin이 Vout을 따라갑니다

2. Switch off - Hold CH에 충전된 전압이 그대로 Vout으로 나타납니다.

Sample을 하면 Vout에 Vin이 그대로 따라와야 하는데 게이트 전압(Vg)가 충분히 높지 않으면 문턱전압으로 인해 Vout에 제한이 생길 수 있습니다. 따라서 실제 switch를 구성할때는 CMOS Switch 를 이용합니다.

또한 clock bootstrapping을 통해 게이트 전압을 VDD+VTH 또는 2VDD+VTH 까지 올려주어 이같은 제한을 완화시켜줄 수도 있습니다.

Switching Noise

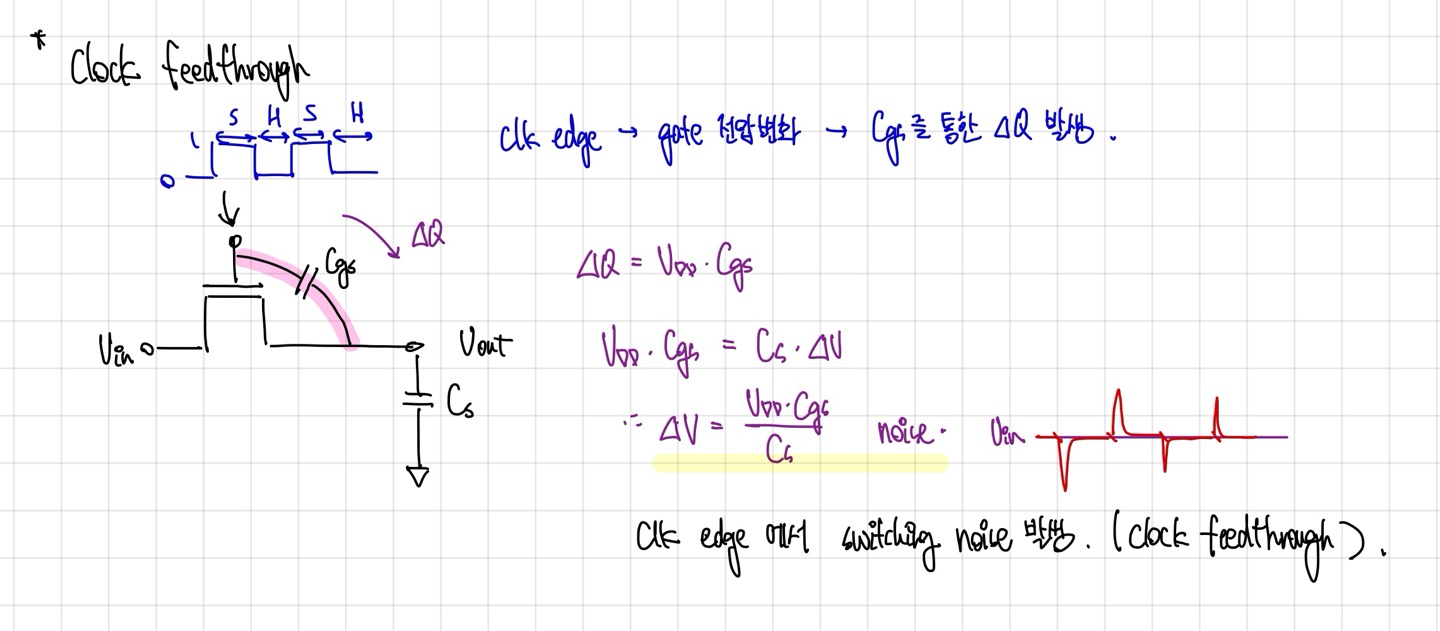

1. Clock Feedthrough

2. Charge Injection

<설계 point> noise ↔ bandwidth trade off

Switching Noise를 줄이기 위해

1. Switch Size↓ → Switch Ron↑

2. Cs Size↑ → RC delay↑

bt 노드 아래 달리는 TR을 먼저 off 시켜서 bt 노드를 floating 상태로 만들어 줄수 있습니다. 이를 통해 Charge injection으로 인한 switching error를 해결해 줍니다.

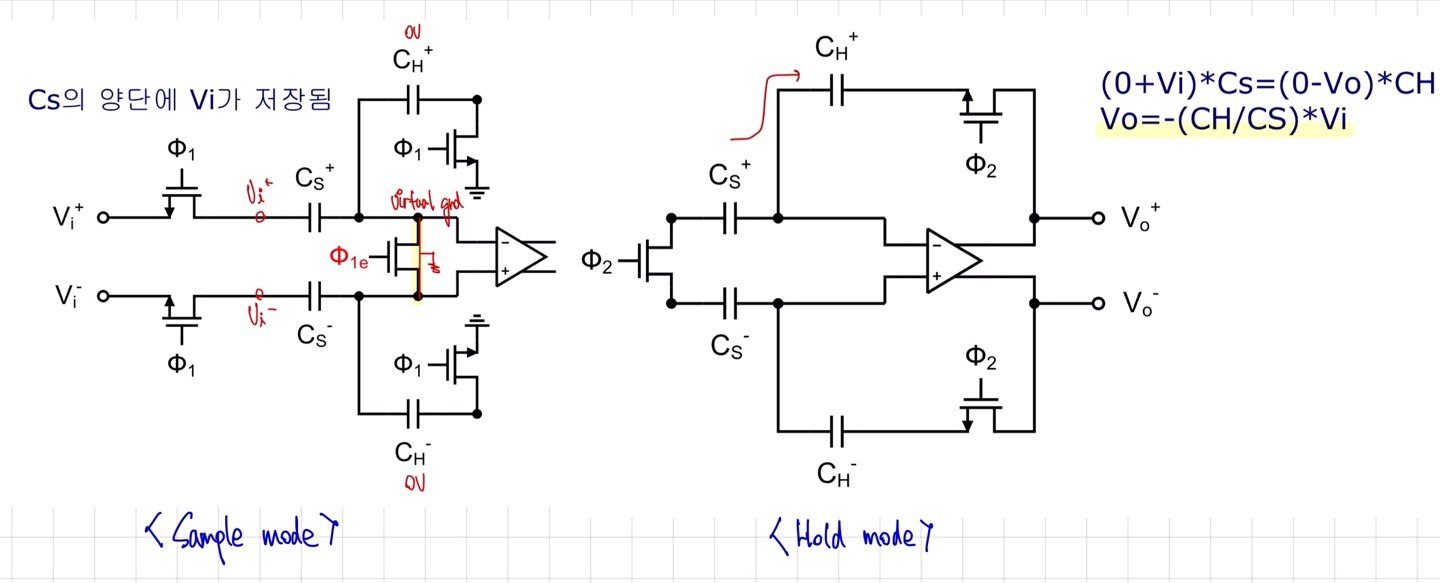

<Sample and Hold Amplifier>

phase 1(sample mode) : Cs에 Vin이 충전된다.

phase 2(hold mode) : Vout = -(Cs/CH)Vi 출력값으로 전달

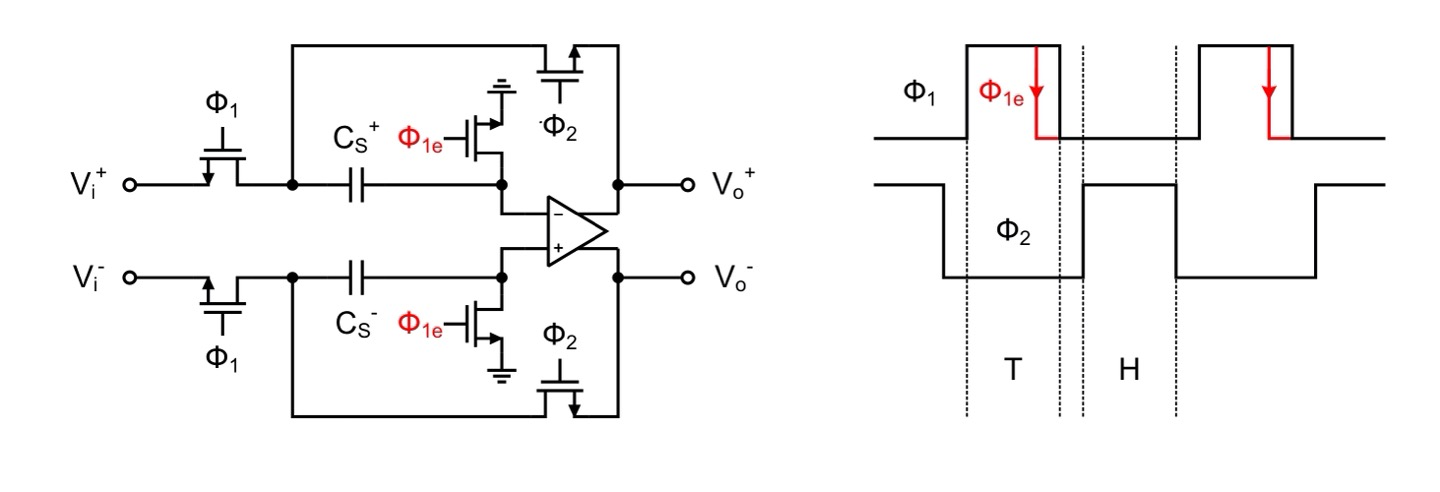

<Non inverting SHA>

phase 1(sample mode) : Cs에 Vin이 충전된다.

phase 2(hold mode) : Vout = -(Cs/CH)Vi 출력값으로 전달 Cs = CH → gain =1

'Analog to Digital Converter' 카테고리의 다른 글

| [설계] 9bit SAR(Successive Approximation Register) ADC (0) | 2024.06.01 |

|---|---|

| [설계] 10bit Charge scaling DAC (1) | 2024.05.25 |

| CMOS Comparator (0) | 2024.03.25 |