Comparator는 '1 bit ADC'라고도 불리는데 아날로그 input을 서로 비교하여 High(VDD) 또는 Low(0)을 출력하는 회로입니다. OP AMP와 유사하지만 비교만 하는 용도로 사용되기 때문에 feedback loop에 따른 frequency compensation등의 작업이 필요로 하지 않습니다. 또한 gain이 non-linear 해도 상관없습니다.

comparator는 빠른 증폭을 통한 빠른 비교가 목적입니다.

<Ideal comparator>

1. High gain

2. low offset (offset은 판정오류를 일으키므로 작을수록 좋다)

3. delay↓ high speed

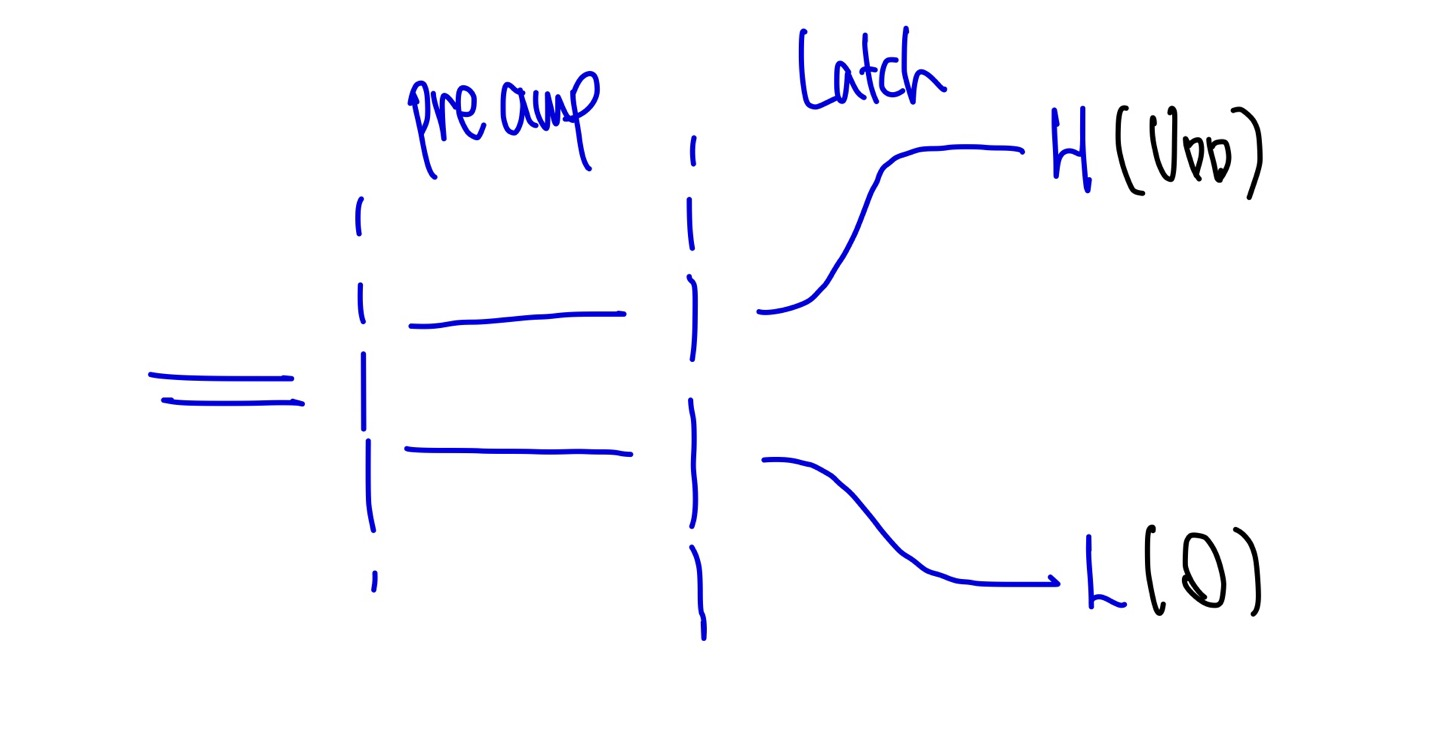

Comparator는 Preamp 와 Latch로 이루어진 2-stage 구조 입니다.

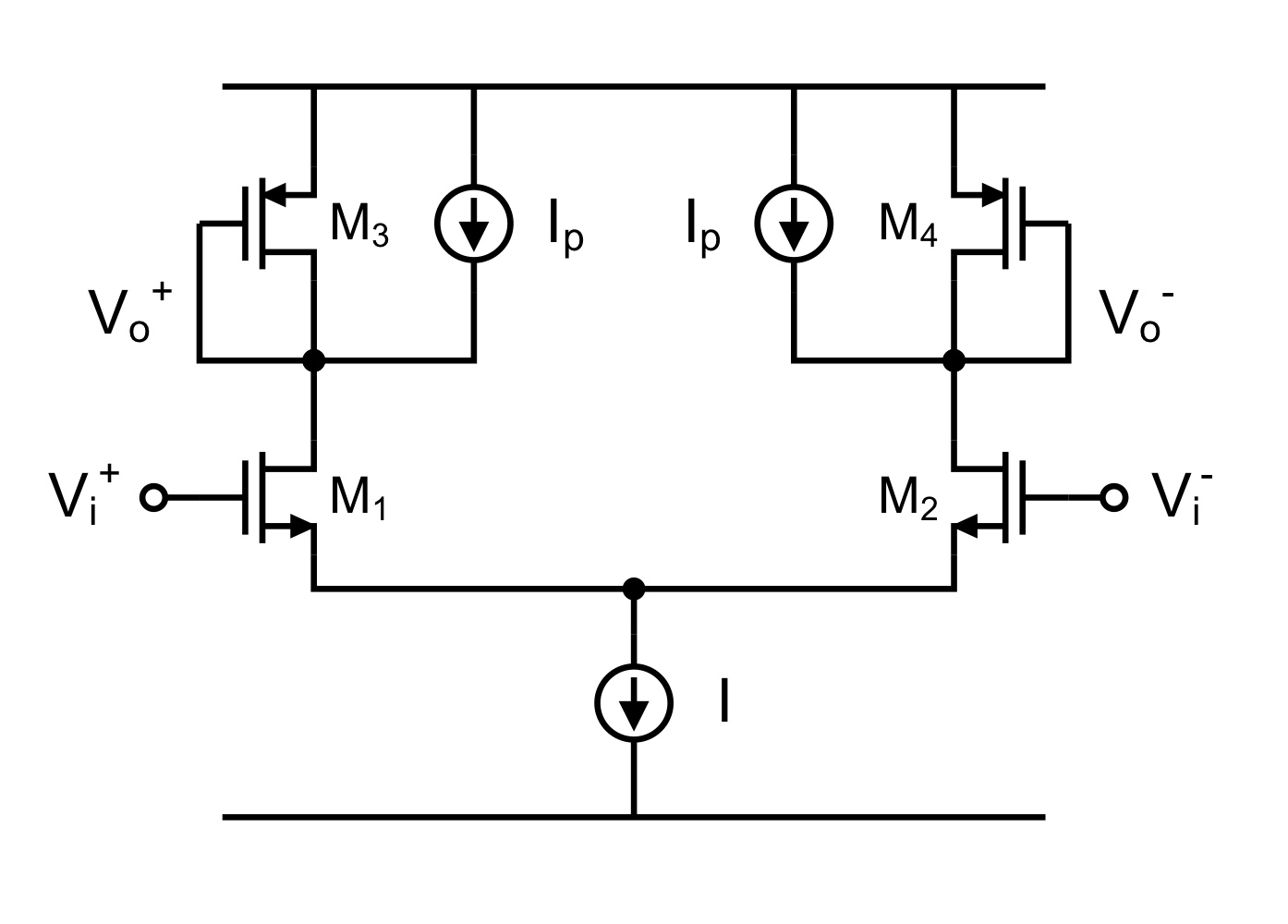

1. Pre amp 의 경우 pmos load를 diode-connected 구조를 활용하여 load에 별도의 biasing 없이 작지만 안정적인 gain을 얻습니다. 하지만 headroom에 부담을 주기때문에 저전력 설계에서는 사용하기 힘들수 있습니다.

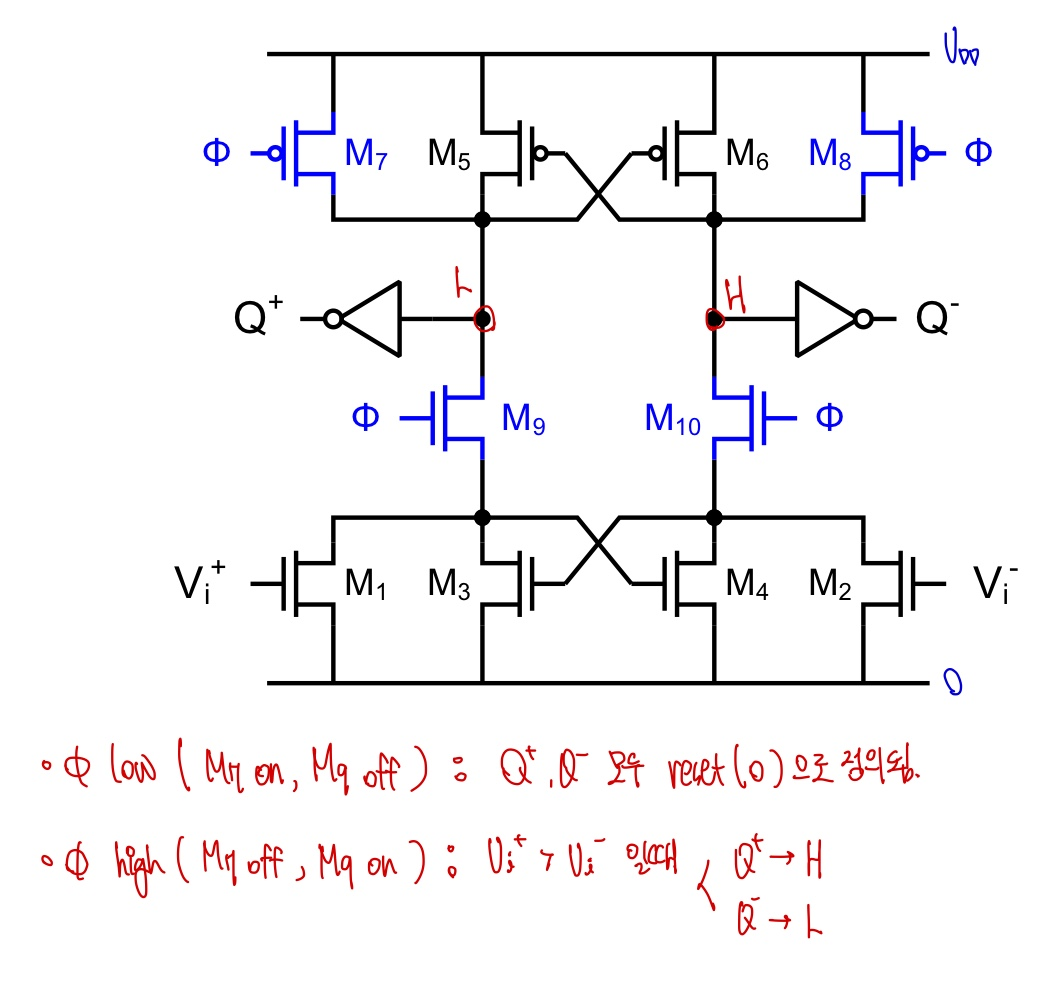

2. Latch에서 M7 과 M8은 cross-coupled pair을 이루고 positive feedback을 통해 빠른 증폭을 얻을 수 있습니다.

위와 같이 preamp를 통해 starting point를 조절하여 metastability를 낮추고 latch에서 빠르게 증폭하여 출력으로 High 또는 low를 뽑아내는 것입니다.

metastability는 Bistable system에서 High/Low를 결정하지 못하는 상태를 말하는데, 이를 개선(감소)시키기 위해서는

comparator의 gain을 키우고, Latch의 입력 신호를 크게 하며, preamp의 offset을 감소하는 것이 중요합니다.

<Pre-amplifier>

기본적으로 diode connected 구조를 이용하여 작지만 안정적인 gain을 얻습니다. 좀더 개선된 형태로 Ip라는 전류원을 이용하여 M3 M4의 전류를 줄이면 이들의 rout을 높일 수 있고 좀더 큰 gain을 얻을 수도 있습니다.

<CMOS Latch>

switch on : Vout을 reset 시키고 CL에 전압을 저장시켜둡니다.

switch off : positive feedback이 동작하며 출력의 양단 전압차를 크게 벌립니다.

이때 NMOS는 pull-down latch, PMOS는 pull-up latch 로 구동합니다.

'Analog to Digital Converter' 카테고리의 다른 글

| [설계] 9bit SAR(Successive Approximation Register) ADC (0) | 2024.06.01 |

|---|---|

| [설계] 10bit Charge scaling DAC (1) | 2024.05.25 |

| Sample and Hold Circuit (0) | 2024.03.18 |