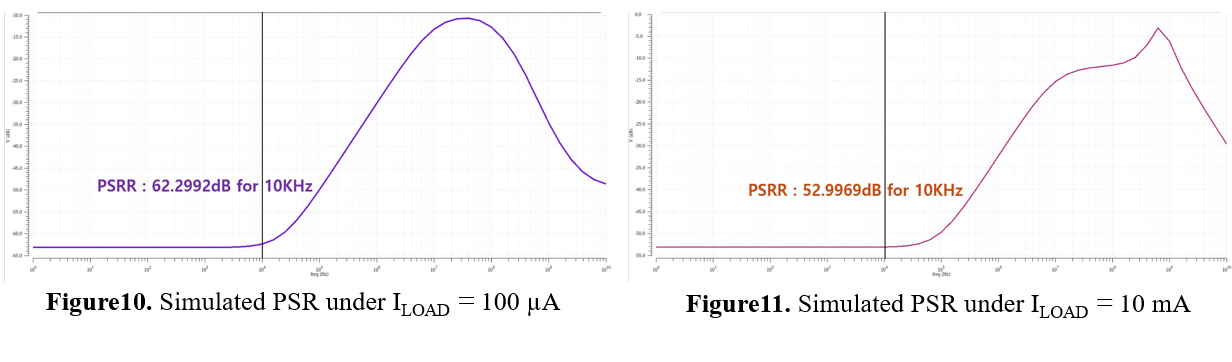

Voltage regulators have been widely used in power management solutions to supply multiple blocks in portable devices. Among the regulators, low-dropout regulators (LDO) is well-known for its fast response, supply ripple rejection, and simple implementation. Conventional LDOs typically utilize an off-chip output capacitor in the µF range to stabilize the system. However, in fully-integrated LDO within system-on-chips (SoCs), the output capacitor value is constrained by the area budget, which can lead to significant degradation in transient response and power-supply rejection (PSR).

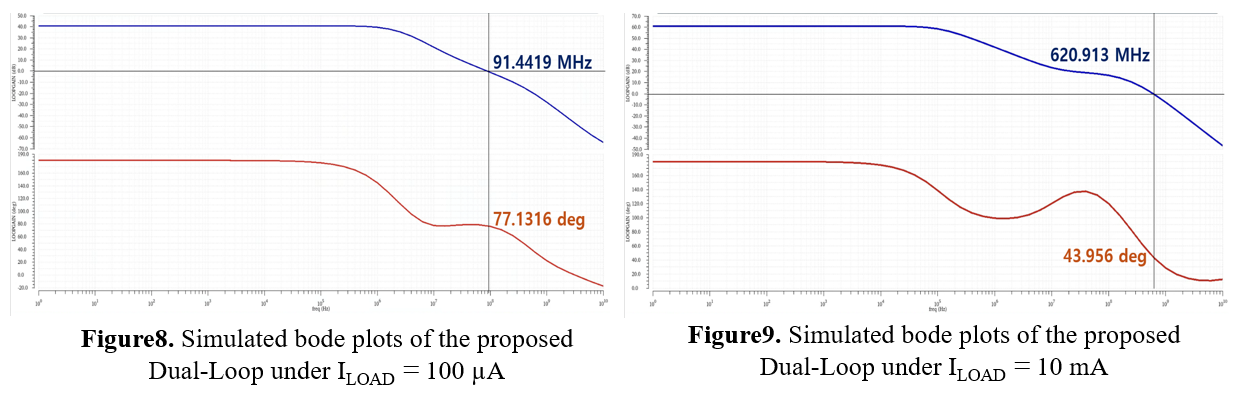

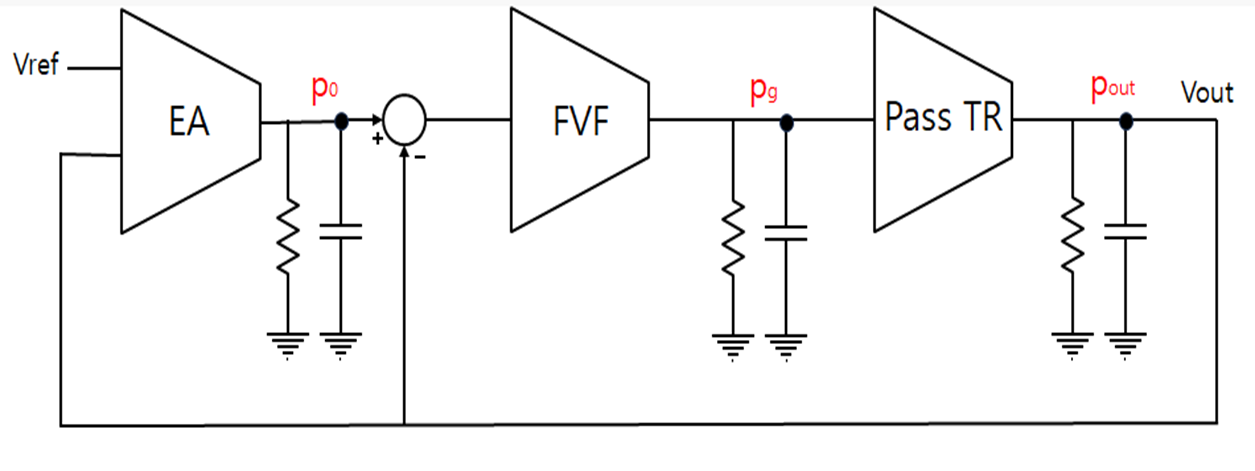

The flipped-voltage-follower LDO (FVF-LDO) offers a simple structure and fast transient response compared to conventional LDO. However, FVF-LDO suffers from poor regulation due to their inherently low DC gain. To address this issue, the proposed FVF-LDO employs a dual-loop technique, placing the dominant pole at the output of EA. This design achieves fast transient response and improved regulation across a wide range of load currents.

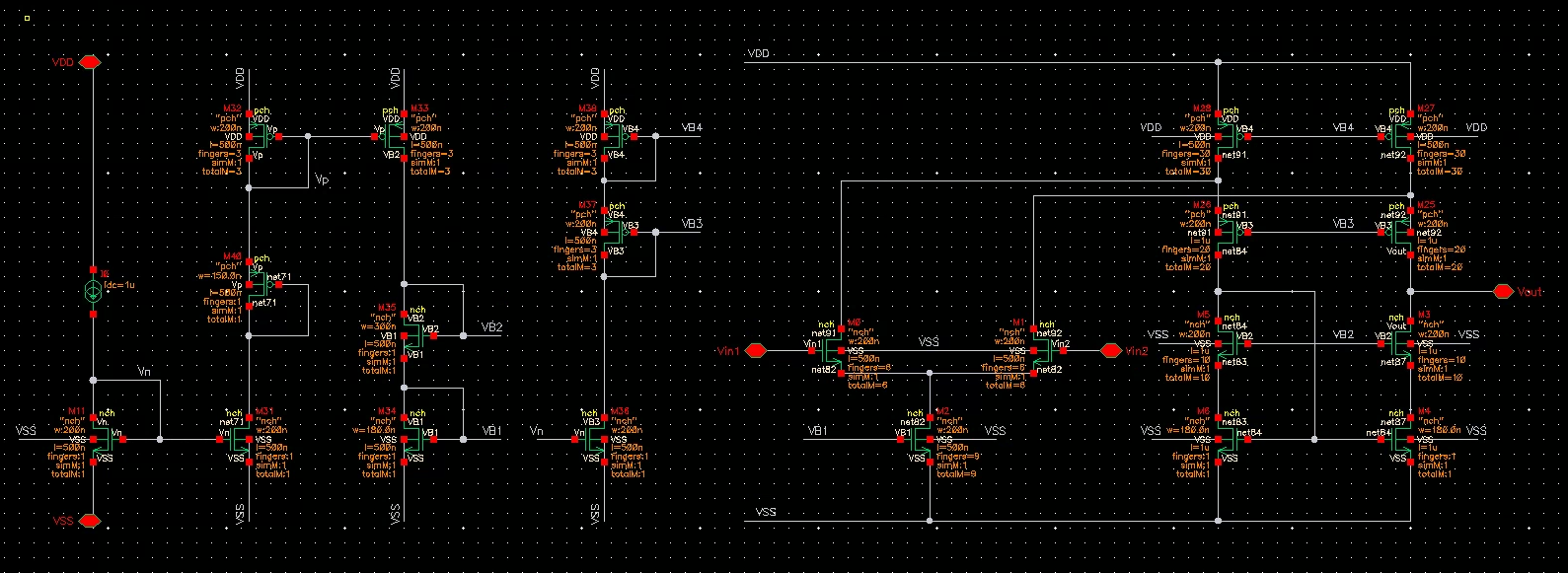

To address the poor load regulation caused by the low DC gain in conventional FVF-LDO, we designed an error amplifier (EA) using a folded cascode structure. This EA, in combination with the FVF-LDO, forms a dual-loop configuration that enhances DC gain, thereby achieving improved load regulation. By incorporating the inherent advantage of the FVF-LDO, the proposed dual-loop system achieves both high DC gain and wide bandwidth.

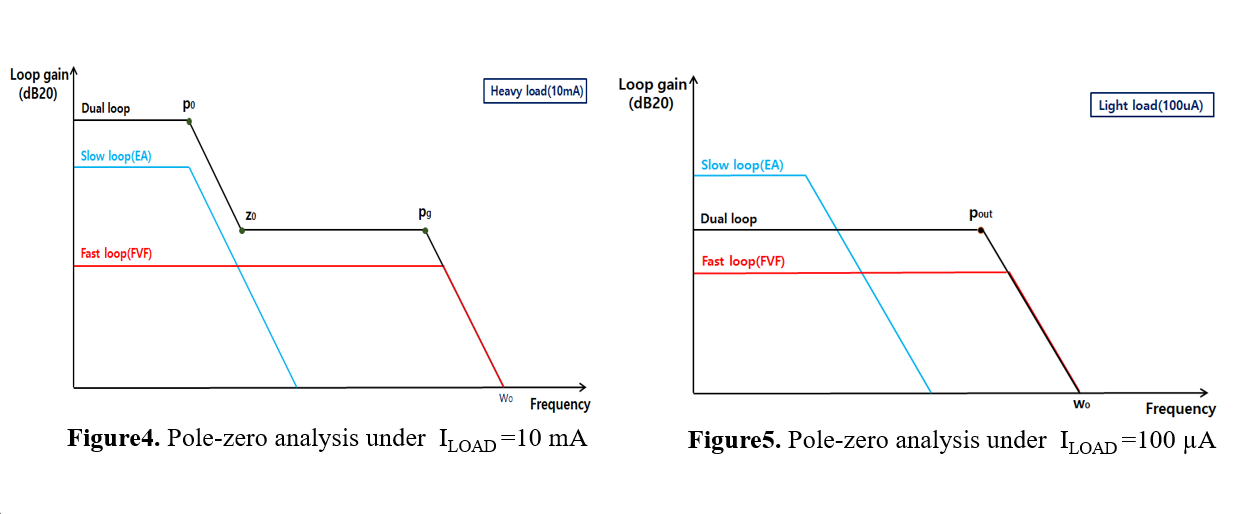

For stability considerations, all non-dominant poles should be moved to frequencies significantly higher than the unity-gain frequency (UGF). The dual-loop system does not require additional frequency compensation because the FVF-LDO loop naturally forms a zero when it interfaces with the EA. In the slow loop, an output capacitor of the EA forms a dominant pole, which is typically at a much lower frequency than the poles in the fast loop. Finally, stability is ensured under both heavy load and light load conditions. By optimizing these design aspects, the proposed dual-loop FVF-LDO demonstrates enhanced load regulation and stability across a wide range of load currents.